“VLSI设计”课程实践教学模式探索

作者: 池雅庆 陈海燕 陈建军

[摘 要] 针对“VLSI设计”课程实践教学中存在关注设计流程、掌握相关EDA工具,但缺乏对先进电路版图设计技术应用和创新实践的问题,提出了基于课前熟悉流程工具、课堂开展归纳分析和课后作业改进创新三个层次的实践教学模式,并以晶体管设计实践课为例,阐述了三个层次的实践教学方法。采用该实践教学模式使学生在熟练掌握全定制物理设计流程的同时,培养了探索创新的思维和追求极致性能的信念,为进一步提高集成电路设计人才的培养质量提供了有益参考。

[关键词] VLSI设计;实践教学;全定制;物理设计

[基金项目] 2020年度国防科技大学研究生教育教学改革研究课题“自主可控信息领域卓越某某领军人才的培养方案研究”(yjsj2020030);2022年度国防科技大学教学成果立项培育项目“面向先进工艺全流程的超大规模集成电路专业课程建设”(jxcg2022187)

[作者简介] 池雅庆(1982—),男,重庆人,博士,国防科技大学计算机学院副研究员,主要从事高性能高可靠集成电路设计研究;陈海燕(1967—),女,四川南充人,硕士,国防科技大学计算机学院研究员,主要从事高性能微处理器技术研究;陈建军(1983—),男,贵州毕节人,博士,国防科技大学计算机学院副研究员,主要从事高速高性能集成电路设计研究。

[中图分类号] G642.0 [文献标识码] A [文章编号] 1674-9324(2023)21-0140-04 [收稿日期] 2023-01-11

引言

集成电路是信息产业的核心,孕育了大量的新兴产业,并为传统产业注入了新的动力,极大地提高了人们的劳动生产率。各国在集成电路领域的竞争十分激烈,尤其是高性能微处理器等高端集成电路产品,国内屡遭西方国家技术封锁,面临着严峻的“卡脖子”问题。而高端集成电路设计人才的匮乏,则是阻碍我国集成电路产业自立自强、突破封锁的关键问题之一,亟须大量基础理论扎实、工程实践能力强的高端集成电路设计和创新人才[1]。人力资源服务供应商前程无忧发布的《2021年Q1“芯力量”(集成电路半导体)市场供需报告》显示,中国的集成电路行业人才缺口巨大,2021年3月人才需求量占集成电路全行业总职位量的比例为5.5%,在行业中位列第四[2]。

我校高端集成电路设计人才培养主要依托计算机学院微电子与固体电子学研究生专业展开。学院长期从事超级计算机研制,在高性能微处理器设计领域处于国内领先水平,研制的飞腾系列微处理器在超级计算机及各类自主可控信息系统中得到了大量应用,相关科研工程实践为高端集成电路设计人才的培养提供了重要支撑[3]。

作为学院微电子与固体电子学研究生专业的核心课,VLSI(Very Large Scale Integrated Circuit 超大规模集成电路)设计承担了复杂数字集成电路,从电路设计直至版图设计的后端物理设计理论与方法的教学任务,培养了一大批能够熟练开展高性能数字集成电路物理设计的人才。VLSI设计教学包括理论教学和实践教学。理论教学分为基本单元、电路设计和系统设计三个模块,主要探讨复杂数字集成电路的设计方法,关注深亚微米以及纳米工艺下先进电路和版图的设计技术,并着重分析影响集成电路性能、功耗和面积的设计参数和优化途径。实践教学主要围绕全定制物理设计展开,从晶体管、导线到组合逻辑单元、时序逻辑单元,直至运算单元和存储器开展设计验证,自下向上全定制构建出完整的功能模块。这需要在有限的教学时间内使学生掌握全定制物理设计的基本流程,熟练运用EDA(Electronic Design Automation,电子设计自动化)工具,并完成功能模块设计[4]。

不同于模拟集成电路设计领域的发展主要依靠电路和版图的不断创新而非半导体工艺的进步,数字集成电路领域的发展长期依赖于半导体工艺的持续进步。工艺进步带来的高性价比使后端物理设计更加聚焦于支持更为先进工艺的复杂物理设计流程,而对于创新电路和版图所获取高性价比的努力有所忽略。反映在“VLSI设计”课程上,尽管理论教学涉及了先进的电路版图设计及优化途径,但实践教学重点关注全定制物理设计流程和相关EDA工具的掌握,缺乏对先进电路版图设计技术的应用和思考[5]。随着某些西方国家对我国先进集成电路工艺封锁的不断加深,在今后相当长一段时间内集成电路工艺水平进步受阻的状态下,创新设计更加优秀的电路和版图是实现数字集成电路性能不断提升的必由之路。

为使“VLSI设计”课程的实践教学更加适应高端数字集成电路发展的现状,本文在VLSI设计实践教学中融入理论分析和创新思考,使学生在熟练掌握全定制物理设计流程的同时,树立追求极致性能的信念,为探索进一步提高集成电路物理设计人才培养质量的方法提供了参考。

一、实践教学模式设计

(一)实践教学模式整体设计

“VLSI设计”课程共54学时,其中理论课36学时,实践课18学时,每次课3学时。实践课包括6次课,分别是晶体管、导线、组合逻辑单元、时序逻辑单元、运算单元和存储器的设计与验证。在18学时的课内时间,对于完全熟悉各类单元的设计验证流程及相关EDA工具的使用已显不足,更遑论开展分析比较和改进创新[6]。

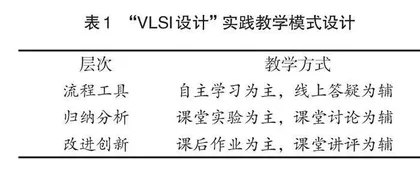

为了在一个学期内使学生具备基本的全定制设计验证能力,并树立追求卓越的信念,我们将每次实践课的教学模式分为流程工具、归纳分析和改进创新三个层次。流程工具层次旨在训练学生掌握全定制设计的基本流程和相关EDA工具的使用方法,完成电路版图设计、仿真验证与规则检查;归纳分析层次旨在训练学生理解集成电路设计要素的特点和规律,培养分析比较设计指标和参数的能力;改进创新层次旨在培养学生基于理论知识指导设计优化实践的能力,树立追求卓越的理念。对不同层次的实践内容分别采取自主学习、线上答疑、课堂讨论和课后作业等教学方式,如表1所示,不仅突出了教学重点,而且提升了教学质量,取得了良好的教学效果。

(二)流程工具层次

流程工具层次实践课的教学目标是使学生掌握集成电路全定制设计的基本流程和相关EDA工具的使用方法,完成给定电路版图的设计、仿真验证与规则检查。

设计流程及配套EDA工具的掌握作为集成电路设计的基本技能,培训资料广泛易得,各EDA工具均提供了详细的培训教程供相关工程师学习,网上也有大量相关知识方便查询。因此,流程工具层次的教学方法以自主学习为主、线上答疑为辅。在每次实践课开始前一周发放本次实践课所使用的EDA环境、工艺规则及操作指导等资料,并建立答疑微信群,学生根据资料在课前完成设计的基本流程和EDA工具的学习,复现操作指导书中指定的操作,获得正确结果。当有任何疑问,可以在微信群中提问答疑,学生之间也可以互相讨论,加深理解[7]。

通过采用自主学习的方式来掌握流程工具知识,不仅为实践课教学质量的提升奠定了基础,也培养了研究生的自学和科研能力。

(三)归纳分析层次

归纳分析层次实践课的教学目标是使学生从实践中发现不同设计变量的输出特征及变化规律,并分析理解其中的理论机制,在掌握基本设计流程的基础上将理论与实际联系起来,拓宽视野,积累经验。

完成全部的设计验证和规则检查流程仅仅是基础,按此方式培养的集成电路设计工程师往往只能机械地执行设计流程,但是如果最终的性能不能满足指标要求,往往无能为力,既不知道设计不足的原因,又不知道怎样寻求改进,甚至不清楚是否能够达到指标。为此,归纳分析层次的实践教学将重点展示各类设计所能达到的性能边界及其不足,使学生将理论学习的知识与实际设计联系起来,了解各类设计的机理和所能达到的综合效果,积累设计经验。教学方法以课堂实验为主、课堂讨论为辅。课堂上教师提供多种设计变量,学生按照设计变量改造流程工具层次已实现的基本设计,并进行仿真,归纳仿真结果的变化规律,分析其变化原因,并在课堂上对其内在理论机制展开讨论,加深理解[8]。

通过采用课堂实验和讨论的方式来对设计效果进行归纳和分析,可以促使学生将理论与实践紧密结合起来,理解设计结果的来源,达到积累设计经验的效果。

(四)改进创新层次

改进创新层次实践课的教学目标是学生能够锻炼学生理论联系实际的能力,综合运用各种手段完成全定制电路版图模块的设计、仿真验证和规则检查,并达到预定的设计指标,形成独立设计和改进全定制数字集成电路并不断追求卓越的能力。

通过在课堂上对各类设计参数和能力的归纳、分析、讨论,学生会发现理论指导实践的魔力,逐渐建立起自己的设计思维,并对改造世界跃跃欲试。改进创新层次将提出若干设计参数目标,引导学生利用已掌握的理论知识改进课堂上分析过的设计,并鼓励学生探索创新,追求卓越。教学方法采用课后作业为主、课堂讲评为辅。当在课堂上完成某模块多种设计结构的评估和分析后,提出一个或多个合适的指标作为课后作业的目标,对该模块进行改进,不限制指标的上下限。对于掌握较慢的学生,竭尽其所能有所收获即可;对于学有余力的学生,则鼓励其追求极致,达到因材施教的效果。课后作业在下一次课前几天提交,教师批改分析后在课堂上讲评,分析改进的思路和理论机制,并探讨学生提出的新思想[9]。

二、以晶体管设计实践课为例

上述内容讲述了“VLSI设计”课程实践教学模式探索的基本思路,下面以晶体管设计实践课为例,详细阐述流程工具、归纳分析和改进创新三个层次的教学。

在流程工具层次,课前一周会发放基于学校信息化云平台的EDA服务器访问方式、相关EDA软件使用说明、PDK(Process Design Kit,工艺设计套件)以及包括晶体管电路版图的绘制方法、电学特性仿真方法、DRC(Design Rule Check,设计规则检查)等规则检查方法在内的实践指导书,并建立答疑微信群。学生需要在课前根据实践指导书登录EDA服务器、绘制晶体管电路版图、仿真电学特性曲线、完成规则检查等。如有问题可以在答疑微信群询问,由助教老师或同学互助解决。实践指导书会推荐晶体管的基本尺寸,但学生绘制版图时在源漏和阱间距等方面仍可能违反DRC规则,因此学生需要根据EDA工具报错的指引,根据实践指导书的指导,借助答疑微信群,甚至上网搜索相关方法,修改使其符合规则。EDA服务器24小时运行,学生可以在任意时间登录操作,通过长时间的上机锻炼,学生能够熟悉设计流程和EDA工具的操作技能。

在归纳分析层次,课堂上会让学生设计不同尺寸的晶体管,在多种工艺角仿真其静态和动态特性,归纳其变化规律,讨论内在的机理机制,使学生理解晶体管尺寸结构、工作电压、工作温度等因素对其饱和电流、开关延迟等电学特性的实际影响和内在机理[10]。

在改进创新层次,布置一项课后作业,设计一个在指定激励和负载下具有最短延迟的反相器电路和版图,完成各工艺角下的延迟仿真,通过DRC等规则检查,提交作业报告。尽管在课堂上已经设计分析了多种晶体管尺寸的反相器延迟,但对于指定的激励和负载并非最优设计。学生需要根据课堂讨论和分析,利用理论指导设计,力争进一步降低延迟。教师通过批改作业,了解学生对晶体管理论知识和实践技能的掌握情况,并在下一次课上总结分析学生使用的改进方法,探讨更多可能的改进方式,巩固教学成果。

结语

培养具有创新能力的高端集成电路设计人才是我国集成电路产业创新发展的关键。通过课前熟悉流程工具、课中开展归纳分析和课后作业改进创新三个层次设计“VLSI设计”课程实践教学模式,并融入理论分析和创新思考,使学生在熟练掌握全定制物理设计流程的同时建立探索创新的思维和追求极致性能的信念,为进一步提高集成电路物理设计人才的培养质量提供了有益参考。

参考文献

[1]国务院.关于印发新时期促进集成电路产业和软件产业高质量发展若干政策的通知:国发〔2020〕8号[A/OL].(2020-07-27)[2022-12-21].http://www.gov.cn/gongbao/content/2020/content_5535318.htm.